- 您现在的位置:买卖IC网 > Sheet目录1905 > ATMEGA48PA-MMNR (Atmel)MCU AVR 4KB FLASH 20MHZ 28QFN

167

8161D–AVR–10/09

ATmega48PA/88PA/168PA/328P

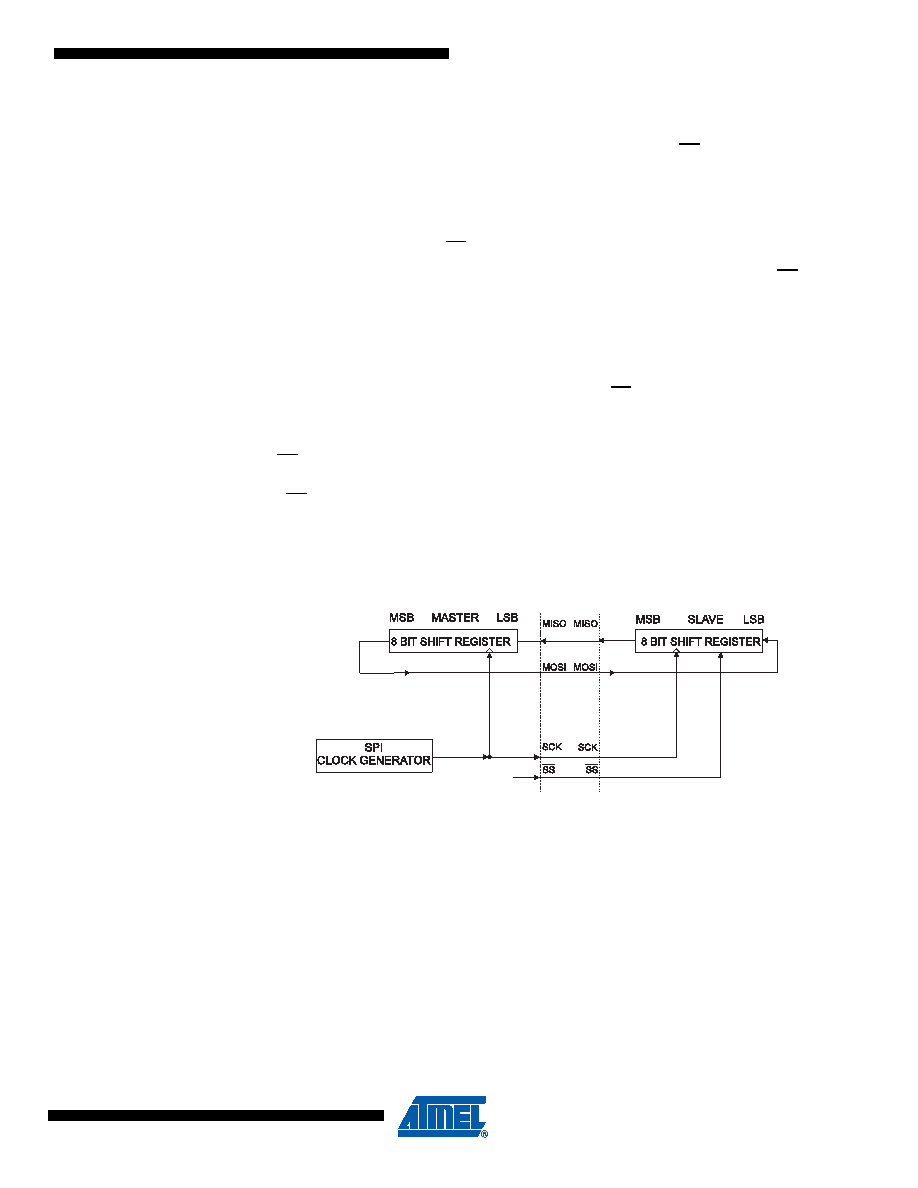

The interconnection between Master and Slave CPUs with SPI is shown in Figure 18-2 on page

167. The system consists of two shift Registers, and a Master clock generator. The SPI Master

initiates the communication cycle when pulling low the Slave Select SS pin of the desired Slave.

Master and Slave prepare the data to be sent in their respective shift Registers, and the Master

generates the required clock pulses on the SCK line to interchange data. Data is always shifted

from Master to Slave on the Master Out – Slave In, MOSI, line, and from Slave to Master on the

Master In – Slave Out, MISO, line. After each data packet, the Master will synchronize the Slave

by pulling high the Slave Select, SS, line.

When configured as a Master, the SPI interface has no automatic control of the SS line. This

must be handled by user software before communication can start. When this is done, writing a

byte to the SPI Data Register starts the SPI clock generator, and the hardware shifts the eight

bits into the Slave. After shifting one byte, the SPI clock generator stops, setting the end of

Transmission Flag (SPIF). If the SPI Interrupt Enable bit (SPIE) in the SPCR Register is set, an

interrupt is requested. The Master may continue to shift the next byte by writing it into SPDR, or

signal the end of packet by pulling high the Slave Select, SS line. The last incoming byte will be

kept in the Buffer Register for later use.

When configured as a Slave, the SPI interface will remain sleeping with MISO tri-stated as long

as the SS pin is driven high. In this state, software may update the contents of the SPI Data

Register, SPDR, but the data will not be shifted out by incoming clock pulses on the SCK pin

until the SS pin is driven low. As one byte has been completely shifted, the end of Transmission

Flag, SPIF is set. If the SPI Interrupt Enable bit, SPIE, in the SPCR Register is set, an interrupt

is requested. The Slave may continue to place new data to be sent into SPDR before reading

the incoming data. The last incoming byte will be kept in the Buffer Register for later use.

Figure 18-2. SPI Master-slave Interconnection

The system is single buffered in the transmit direction and double buffered in the receive direc-

tion. This means that bytes to be transmitted cannot be written to the SPI Data Register before

the entire shift cycle is completed. When receiving data, however, a received character must be

read from the SPI Data Register before the next character has been completely shifted in. Oth-

erwise, the first byte is lost.

In SPI Slave mode, the control logic will sample the incoming signal of the SCK pin. To ensure

correct sampling of the clock signal, the minimum low and high periods should be:

Low periods: Longer than 2 CPU clock cycles.

High periods: Longer than 2 CPU clock cycles.

SHIFT

ENABLE

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ATMEGA644P-B15MZ

IC MCU 8BIT 64KB FLASH 32VQFN

ATMEGA644V-10PU

IC AVR MCU FLASH 64K 40DIP

ATMEGA645V-8MI

IC AVR MCU FLASH 64K 1.8V 64QFN

ATMEGA649-16MI

IC AVR MCU FLASH 64K 5V 64QFN

ATMEGA649V-8MI

IC AVR MCU FLASH 64K 1.8V 64QFN

ATMEGA8515L-8JUR

MCU AVR 8KB FLASH 8MHZ 44PLCC

ATMEGA8515L-8PJ

IC MCU AVR 8K 5V 8MHZ 40-DIP

ATMEGA8535-16JUR

MCU AVR 8K FLASH 16MHZ 44PLCC

相关代理商/技术参数

ATMEGA48PA-MN

功能描述:8位微控制器 -MCU AVR 4KB FL 256B EE 512B SRAM 20MHz 105C RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA48PA-MNR

功能描述:8位微控制器 -MCU AVR 4KB FL 256B EE 512B SRAM 20MHz 105C RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA48PA-MU

功能描述:8位微控制器 -MCU AVR 4KB FLASH 20 MHZ,IND TEMP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA48PA-MU@SL383

制造商:Atmel 功能描述:MCU 8-bit ATmega AVR RISC 4KB Flash 2.5V/3.3V/5V 32-Pin QFN EP T/R

ATMEGA48PA-MUR

功能描述:8位微控制器 -MCU AVR 4KB FLSH 256B EE 512B SRAM-20MHz IND RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA48PA-PN

功能描述:8位微控制器 -MCU AVR 4KB FL 256B EE 512B SRAM 20MHz 105C RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA48PA-PU

功能描述:8位微控制器 -MCU AVR 4KB FLASH 20 MHZ,IND TEMP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA48PB-AN

功能描述:AVR AVR? ATmega Microcontroller IC 8-Bit 20MHz 4KB (2K x 16) FLASH 32-TQFP 制造商:atmel 系列:AVR? ATmega 包装:托盘 零件状态:有效 核心处理器:AVR 核心尺寸:8-位 速度:20MHz 连接性:I2C,SPI,UART/USART 外设:欠压检测/复位,POR,PWM,WDT I/O 数:27 程序存储容量:4KB(2K x 16) 程序存储器类型:闪存 EEPROM 容量:256 x 8 RAM 容量:512 x 8 电压 - 电源(Vcc/Vdd):1.8 V ~ 5.5 V 数据转换器:A/D 8x10b 振荡器类型:内部 工作温度:-40°C ~ 105°C(TA) 封装/外壳:32-TQFP 供应商器件封装:32-TQFP 标准包装:250